# UNIVERSIDADE FEDERAL DE SANTA MARIA CENTRO DE TECNOLOGIA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

Rafael Gauna Trindade

ESCALONADOR ADAPTATIVO PARA LAÇOS PARALELOS EM PROCESSADORES MULTINÚCLEO ASSIMÉTRICOS

## Rafael Gauna Trindade

# ESCALONADOR ADAPTATIVO PARA LAÇOS PARALELOS EM PROCESSADORES MULTINÚCLEO ASSIMÉTRICOS

Dissertação de Mestrado apresentada ao Programa de Pós-Graduação em Ciência da Computação, Área de Concentração em Ciência da Computação, da Universidade Federal de Santa Maria (UFSM, RS), como requisito parcial para obtenção do grau de **Mestre em Ciência da Computação**. Defesa realizada por videoconferência.

ORIENTADOR: Prof. João Vicente Ferreira Lima

Trindade, Rafael Gauna

Escalonador Adaptativo para Laços Paralelos em

Processadores Multinúcleo Assimétricos / Rafael Gauna

Trindade. - 2020.

72 p.; 30 cm

Orientador: João Vicente Ferreira Lima Dissertação (mestrado) - Universidade Federal de Santa Maria, Centro de Tecnologia, Programa de Pós-Graduação em Ciência da Computação , RS, 2020

1. Algoritmos Adaptativos 2. Escalonadores 3. Laços Paralelos 4. Processadores Multinúcleo Assimétricos 5. Computação Paralela I. Ferreira Lima, João Vicente II. Título.

Sistema de geração automática de ficha catalográfica da UFSM. Dados fornecidos pelo autor(a). Sob supervisão da Direção da Divisão de Processos Técnicos da Biblioteca Central. Bibliotecária responsável Paula Schoenfeldt Patta CRB 10/1728.

Declaro, RAFAEL GAUNA TRINDADE, para os devidos fins e sob as penas da lei, que a pesquisa constante neste trabalho de conclusão de curso (Dissertação) foi por mim elaborada e que as informações necessárias objeto de consulta em literatura e outras fontes estão devidamente referenciadas. Declaro, ainda, que este trabalho ou parte dele não foi apresentado anteriormente para obtenção de qualquer outro grau acadêmico, estando ciente de que a inveracidade da presente declaração poderá resultar na anulação da titulação pela Universidade, entre outras consequências legais.

# ©2020

Todos os direitos autorais reservados a Rafael Gauna Trindade. A reprodução de partes ou do todo deste trabalho só poderá ser feita mediante a citação da fonte.

End. Eletr.: rtrindade@inf.ufsm.br

#### Rafael Gauna Trindade

# ESCALONADOR ADAPTATIVO PARA LAÇOS PARALELOS EM PROCESSADORES MULTINÚCLEO ASSIMÉTRICOS

Dissertação de Mestrado apresentada ao Programa de Pós-Graduação em Ciência da Computação, Área de Concentração em Ciência da Computação, da Universidade Federal de Santa Maria (UFSM, RS), como requisito parcial para obtenção do grau de Mestre em Ciência da Computação.

Aprovado em 30 de março de 2020:

João Vicente Ferreira Lima, Dr. (UFSM)

Andrea Schwertner Charão, Dra. (UFSM)

Leonardo Fialho de Queiroz, PhD. (Atos)

# **DEDICATÓRIA** Dedico este trabalho a todos os(as) pesquisadores(as) e demais profissionais da ciência, que trabalham continuamente em prol do conhecimento, destacando uma das melhores características do ser humano: a curiosidade.

#### **AGRADECIMENTOS**

Agradeço primeiramente aos meus pais e irmãos, pelo amor, atenção e apoio incondicional que prestaram durante a pós-graduação e também durante toda a minha vida.

Agradeço ao meu professor orientador, João, e aos professores que comporam a banca, Andrea e Leonardo, que contribuíram de forma insubstituível para a minha formação e a de meus colegas de programa.

Agradeço pelo companheirismo e força passados pelos meus amigos e colegas de Laboratório, com os quais convivi durante estes dois anos no Laboratório de Sistemas de Computação. Agradecimentos especiais aos mais próximos: Ana, Bruno, Iago, Lucas e Maurício.

Agradeço aos meus demais amigos, que me acompanharam e me deram forças desde o começo. Agradecimentos especiais aos mais próximos: Amanda, Bruna, Caroline, Cassiano, Felipe, João, Laura, Linda, Márian, Otávio, Pedro, Raul e Vinícius.

Por fim, agradeço à Universidade Federal de Santa Maria, pelo ambiente de ensino de excelência, amigável e acolhedor que proporciona aos seus alunos e que me proporcionou durante esses dois anos de programa.

Do not parallelize what does not matter! I talked it to too many users who just parallelized every loop in their program... that's not a good idea, all right?

(Ruud van der Pas, 2019)

# **RESUMO**

# ESCALONADOR ADAPTATIVO PARA LAÇOS PARALELOS EM PROCESSADORES MULTINÚCLEO ASSIMÉTRICOS

AUTOR: Rafael Gauna Trindade ORIENTADOR: João Vicente Ferreira Lima

A crescente demanda por potência computacional e eficiência energética em computação móvel desencadeou o desenvolvimento de processadores heterogêneos com núcleos especializados para diferentes tipos de tarefas computacionais, como processadores ARM big.LITTLE, que tem núcleos distintos que aliam desempenho a baixo consumo energético. Tal diferença na composição dos núcleos nesse tipo de processadores acaba induzindo uma assimetria no desempenho computacional desses sistemas, tornando complicada a tarefa de prever o comportamento de aplicações paralelas com relação a desempenho quando usados todos os seus núcleos. Essa assimetria pode ser percebida em aplicações que façam uso de laços paralelos, um recurso de programação paralela que permite dividir a carga de trabalho de uma rotina iterativa entre os núcleos presentes em um processador. Escalonadores de laços paralelos que não são projetados de modo a evitar a perda de desempenho em processadores multinúcleo assimétricos (AMPs) podem comprometer a implementação de soluções de software construídas para esse tipo de arquitetura. Esta dissertação apresenta a proposta de implementação de um escalonador para laços paralelos que utiliza um algoritmo adaptativo para distribuição da carga de trabalho entre as threads, visando extrações de desempenho mais eficientes em AMPs. O escalonador utiliza-se de roubo de trabalho paralelo e extração de trabalho sequencial o mais livre de travas quanto for possível para fazer frente às demais soluções existentes. Sua implementação foi realizada na linguagem C++, com possibilidade de portabilidade para a linguagem C. Com a finalidade de avaliar o desempenho da solução, uma análise foi realizada sobre o conjunto de benchmarks NAS e quatro aplicações científicas distintas bem consolidadas na literatura relacionada, sobre dois ambientes assimétricos embarcados reais, contra duas soluções existentes (OpenMP e Intel TBB). A análise mostra que o escalonador consegue extrair mais desempenho em determinados casos e se aproxima muito das melhores soluções na maioria dos casos restantes, com potencial de escalabilidade em teoria maior para casos onde o sobrecusto de escalonamento se torna um empecilho nas demais soluções.

**Palavras-chave:** Algoritmos Adaptativos. Escalonadores. Laços Paralelos. Processadores Multinúcleo Assimétricos. Computação Paralela. Computação Heterogênea. Computação de Alto Desempenho. Roubo de Trabalho. OpenMP. Intel TBB.

# **ABSTRACT**

# AN ADAPTIVE SCHEDULER FOR PARALLEL LOOPS ON ASYMMETRIC MULTICORE PROCESSORS

AUTHOR: Rafael Gauna Trindade ADVISOR: João Vicente Ferreira Lima

The growing demand for computing power and energy efficiency in mobile computing has triggered the development of heterogeneous processors with specialized cores for different types of computational tasks, such as ARM big.LITTLE processors, which have different cores that combine performance with low energy consumption. Such difference in the composition of the cores in this kind of processors ends up inducing an asymmetry in the computational performance of these systems, making complicated the task of predicting the behavior of parallel applications in relation to performance when using all their cores. This asymmetry can be detected in applications that use parallel loops, a parallel programming feature that allows to divide the workload of an iterative routine between the cores present in a processor. Parallel loop schedulers that are not designed to prevent loss of performance in asymmetric multi-core processors (AMPs) can compromise the implementation of software solutions designed for this type of architecture. This dissertation presents the implementation proposal of a scheduler for parallel loops that uses an adaptive algorithm to distribute the workload among the threads, aiming at a better extraction of performance in AMPs. The scheduler uses of parallel work-stealing and lock-free as possible sequential extraction of work to face other existing solutions. Its implementation was carried out in the C ++ language, with the possibility of portability to the C language. In order to evaluate the performance of the solution, an analysis was performed on the set of NAS benchmarks and four distinct well-established scientific applications in related literature, over two real asymmetric embedded environments, against two existing solutions (OpenMP and Intel TBB). The analysis shows that the scheduler is able to extract more performance in certain cases and is very close to the best solutions in most of the remaining cases, with greater scalability potential in theory for cases where the scheduling overhead becomes an obstacle in the other solutions.

**Keywords:** Adaptive Algorithms. Schedulers. Parallel Loops. Asymmetric Multicore Processors. Parallel Computing. Heterogeneous Computing. High Performance Computing. Work Stealing. OpenMP. Intel TBB.

# LISTA DE GRÁFICOS

| Gráfico 2.1 – Aceleração teórica paralela de uma arquitetura paralela heterogênea em |    |

|--------------------------------------------------------------------------------------|----|

| relação à uma homogênea de mesmo custo                                               | 19 |

| Gráfico 2.2 – Tempo de execução do conjunto de benchmarks SPEC OMP                   | 20 |

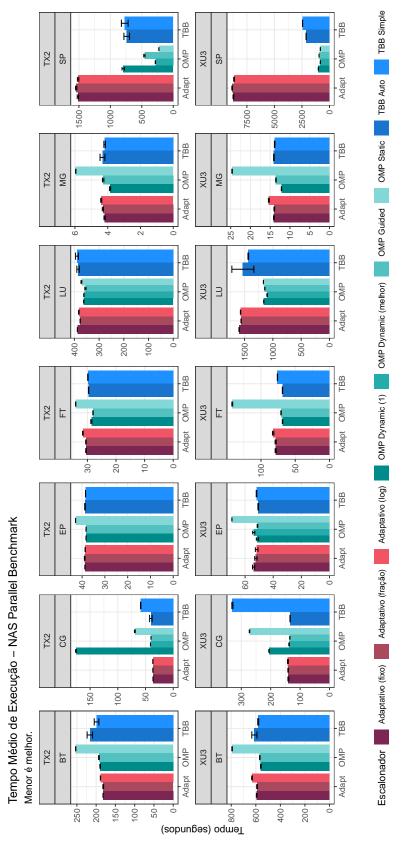

| Gráfico 3.1 – Tempo médio de execução com o NAS Parallel Benchmark                   | 53 |

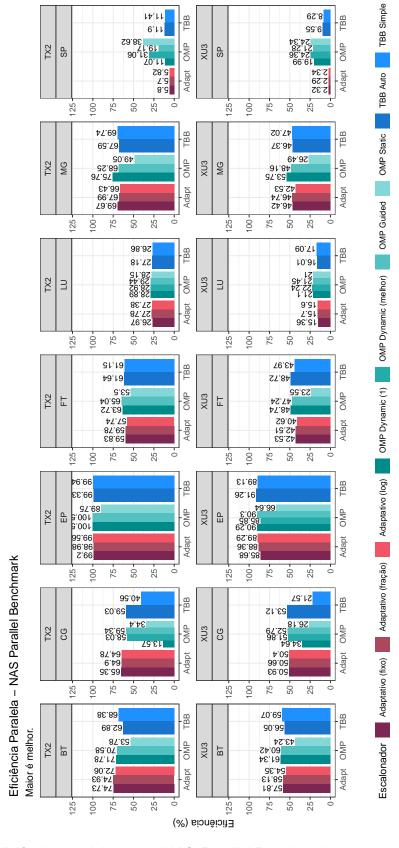

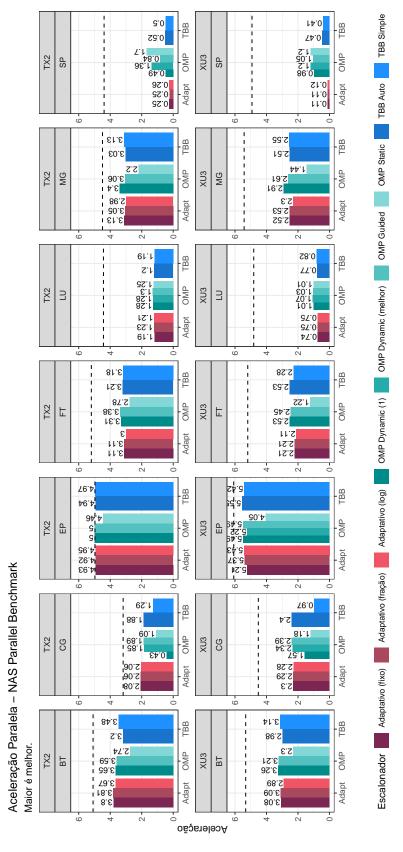

| Gráfico 3.2 – Eficiência paralela com o NAS <i>Parallel Benchmark</i>                | 54 |

| Gráfico 3.3 – Aceleração paralela com o NAS Parallel Benchmark                       | 55 |

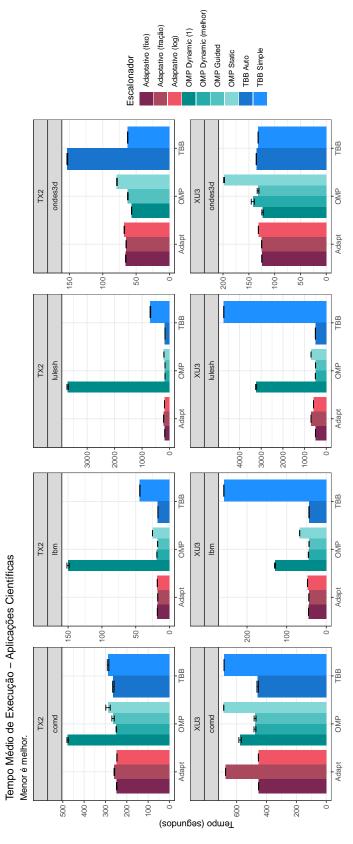

| Gráfico 3.4 - Tempo médio de execução com as aplicações científicas selecionadas .   | 59 |

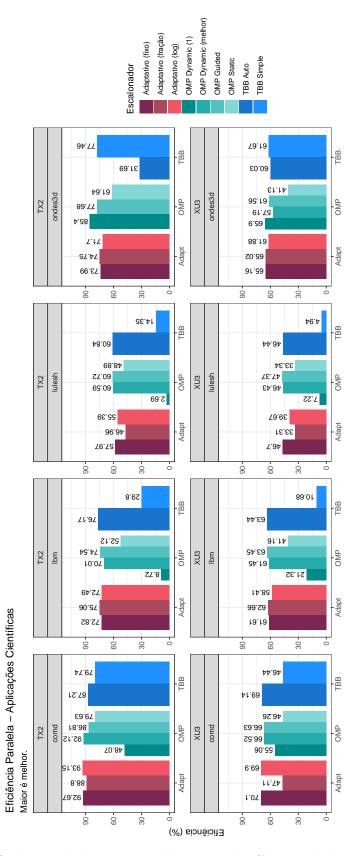

| Gráfico 3.5 – Eficiência paralela com as aplicações científicas selecionadas         | 60 |

| Gráfico 3.6 – Aceleração paralela com as aplicações científicas selecionadas         | 61 |

# LISTA DE ILUSTRAÇÕES

| Ilustração 2.1 – Diagrama da Taxonomia de Flynn e Rudd (1996)                        | 17 |

|--------------------------------------------------------------------------------------|----|

| Ilustração 2.2 – Diagrama exemplo de um AMP                                          | 18 |

| Ilustração 2.3 – Classificação de algoritmos híbridos                                | 22 |

| Ilustração 2.4 – Caso exemplo de paralelização de laço com OpenMP                    | 23 |

| Ilustração 2.5 - Caso exemplo de paralelização de laço com a diretiva taskloop do    |    |

| OpenMP                                                                               | 25 |

| Ilustração 2.6 - Caso exemplo de paralelização de laço com biblioteca Intel TBB      | 26 |

| Ilustração 3.1 – Fluxograma do ciclo de vida de uma thread                           | 34 |

| Ilustração 3.2 - Caso exemplo de extração de trabalho em um sub-intervalo particular | 34 |

| Ilustração 3.3 – Escalonador Adaptativo – Algoritmo de Extração de Trabalho Sequen-  |    |

| cial                                                                                 | 35 |

| Ilustração 3.4 - Caso exemplo de um conflito durante extração de trabalho            | 36 |

| Ilustração 3.5 – Escalonador Adaptativo – Algoritmo de Extração de Trabalho Paralelo | 37 |

| Ilustração 3.6 – Exemplos de divisão inicial e roubo de trabalho                     | 40 |

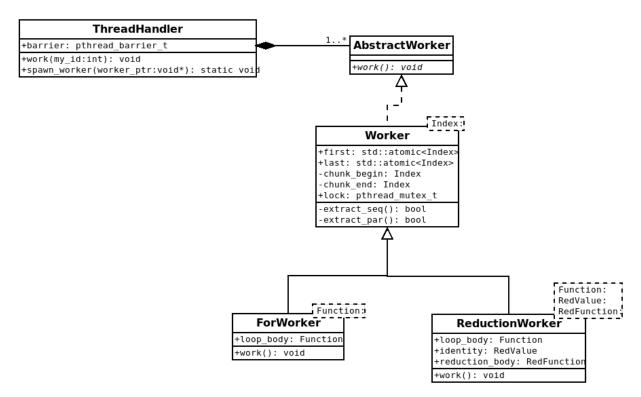

| Ilustração 3.7 - Diagrama UML das classes utilizadas pelo escalonador                | 41 |

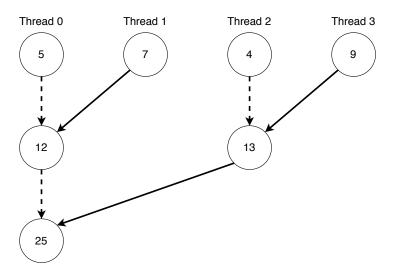

| Ilustração 3.8 - Esquema de redução em árvore empregado pelo escalonador             | 41 |

| Ilustração 3.9 - Comparação de desempenho de tipos atômicos do C++ com outros        |    |

| tipos de trava.                                                                      | 42 |

| Ilustração 3.10 – Assinaturas dos métodos de Iaço e redução paralelas                | 43 |

| Ilustração 3.11 - Caso exemplo de paralelização de laço com a API proposta           | 43 |

# LISTA DE TABELAS

| Tabela | 3.1 – Dispositivos Embarcados Utilizados na Avaliação                     | 48 |

|--------|---------------------------------------------------------------------------|----|

| Tabela | 3.2 – Núcleos de CPU por Configuração de Cluster                          | 48 |

| Tabela | 3.3 – Aplicações e Kernels do NAS Parallel Benchmark Usadas na Avaliação. | 49 |

| Tabela | 3.4 – Aplicações Científicas Usadas na Avaliação                          | 51 |

| Tabela | 3.5 – Tempos de Execução Seguencial dos <i>Benchmarks</i> , em Segundos   | 52 |

# LISTA DE ABREVIATURAS E SIGLAS

| AMP  | Asymmetric Multicore Processor (Processador Multinúcleo Assimétrico) |

|------|----------------------------------------------------------------------|

| APME | Aceleração Paralela Máxima Esperada                                  |

| CPU  | Central Processing Unit (Unidade de Processamento Central)           |

| HPC  | High Performance Computing (Computação de Alto Desempenho)           |

| ISA  | Intruction Set Architeture (Conjunto de Instruções de Arquitetura)   |

| PU   | Processing Unit (Unidade de Processamento)                           |

| SMP  | Symmetric Multicore Processor (Processador Multinúcleo Simétrico)    |

# **SUMÁRIO**

| 1     | INTRODUÇÃO                                   | 13 |

|-------|----------------------------------------------|----|

| 2     | FUNDAMENTAÇÃO TEÓRICA                        |    |

| 2.1   | ARQUITETURAS PARALELAS                       | 15 |

| 2.1.1 | Taxonomia de Arquiteturas Paralelas          |    |

| 2.2   | PROCESSADORES MULTINÚCLEO ASSIMÉTRICOS       | 16 |

| 2.2.1 | ARM big.LITTLE™                              | 17 |

| 2.2.2 | Efeitos da Assimetria no Desempenho          | 18 |

| 2.3   | ALGORITMOS ADAPTATIVOS                       |    |

| 2.4   | ESCALONADORES DE LAÇOS PARALELOS             | 22 |

| 2.4.1 | OpenMP                                       | 23 |

| 2.4.2 | Intel TBB                                    | 25 |

| 2.5   | TRABALHOS RELACIONADOS                       | 27 |

| 2.6   | SUMÁRIO                                      |    |

| 3     | ESCALONADOR ADAPTATIVO                       |    |

| 3.1   | LAÇO PRINCIPAL DO ESCALONADOR                |    |

| 3.2   | ALGORITMOS DE EXTRAÇÃO SEQUENCIAL E PARALELA |    |

| 3.3   | OTIMIZAÇÃO                                   |    |

| 3.4   | IMPLEMENTAÇÃO                                |    |

| 3.4.1 | API para Laços Paralelos                     |    |

| 3.5   | SUMÁRIO                                      |    |

| 3.6   | ANÁLISE DE DESEMPENHO                        |    |

| 3.7   | METODOLOGIA                                  |    |

|       | Métricas                                     |    |

|       | Ambientes                                    |    |

| 3.7.3 | Benchmarks                                   |    |

| 3.8   | RESULTADOS EXPERIMENTAIS                     |    |

|       | Desempenho Sequencial                        |    |

|       | NAS Parallel Benchmark                       |    |

|       | Aplicações Científicas                       |    |

| 3.9   | SUMÁRIO                                      |    |

| 4     | CONCLUSÃO                                    | 64 |

|       | REFERÊNCIAS BIBLIOGRÁFICAS                   | 67 |

# 1 INTRODUÇÃO

Com a demanda crescente da indústria por dispositivos computacionais que combinem boa capacidade de processamento com eficiência energética – um aumento substancial em vendas de smartphones e tablets, por exemplo –, novos tipos de necessidades surgiram, e com elas novas tecnologias de hardware foram propostas para poder suprílas. O hoje antigo conceito de processador multinúcleo simétrico (*Symmetric Multicore Processor*, em inglês – SMP), mesmo com ajustes dinâmicos de consumo de energia e frequência de operação (i.e. DVFS), acaba contido por limitações estruturais uma vez que é difícil criar um núcleo dinâmico o suficiente para acomodar tanto baixo consumo de energia quanto bom poder de processamento. Como uma consequência de sua adaptabilidade à diversidade, Processadores Multinúcleo Assimétricos (*Asymmetric Multicore Processor*, em inglês – AMP) prometem ser benéficos para uma vasta gama de cenários de uso: núcleos diferentes em um AMP podem ser otimizados para consumo/desempenho, ou para diferente domínios de aplicação, ou para explorar diferentes níveis de paralelismo (MITTAL, 2016).

A principal vantagem no uso de AMPs, do ponto de vista de Computação de Alto Desempenho (High Performance Computing, em ingês – HPC) se justamente dá pelas características híbridas de seus núcleos. Tarefas sequenciais ou com o desempenho determinado pelas computações em si (CPU-bound) obterão melhores resultados sendo executados em núcleos rápidos, ao passo que tarefas paralelas ou com o desempenho determinado pelos acessos à memória (memory bound) possuem benefícios em serem executadas em núcleos lentos (FEDOROVA et al., 2009). Estudos anteriores mostram que se é possível ganhar em torno de até 63% de desempenho em comparação a SMPs de mesma área de chip e consumo energético (KUMAR et al., 2004). Em um cenário de computação de alto-desempenho, essa flexibilidade associada a uma maior eficiência energética atrai a atenção, uma vez que esta última é um dos desafios na atual corrida pelo hexascale: construir computadores rápidos que consumam menos energia e realizem mais computações. Assim, em paralelo a já tradicional Top5001 – lista semestral dos 500 supercomputadores mais rápidos do mundo – foi criada a Green500<sup>2</sup>, uma lista dos 500 supercomputadores com a maior taxa de eficiência energética (em bilhões de operações de ponto flutuante (GFlop) por Watt) do mundo, ressaltando a sua importância para a área de HPC. E AMPs possibilitam o melhor destes dois mundos: apesar de possuírem características bem próprias em relação a eficiência energética, não estão limitadas a tal. Como consistem de ambientes de múltiplos núcleos, facilmente se concebe cenários em que abrir mão de eficiência energética em prol de desempenho pode se tornar conveniente.

<sup>1&</sup>lt;http://top500.org>

<sup>&</sup>lt;sup>2</sup><http://green500.org>

Entretanto extrair desempenho destas plataformas pode apresentar desafios devido a assimetria nelas contida. Essa possível diferença em capacidade de processamento entre diferentes tipos de núcleo pode levar a problemas de desempenho se o desenvolvedor de uma aplicação paralela não estiver consciente da assimetria do ambiente onde ela será executada. Durante a criação deste tipo de aplicação, desenvolvedores podem optar por utilizar laços paralelos, uma estratégia de programação paralela que permite dividir a carga de trabalho computacional de uma estrutura iterativa entre os núcleos disponíveis em uma máquina, geralmente de uma forma simples de ser entendida, uma vez que essas estruturas podem ser representadas por um intervalo númerico divisível. Um programador OpenMP, por exemplo, pode escolher entre alguns escalonadores de laços paralelos providos pela especificação da API e implementados em diferentes versões da *runtime* distribuídas em diferentes compiladores (GCC, LLVM, ICC, Nanos, IBM XL, entre outros). Entretanto, o uso descuidado desses escalonadores pode criar problemas de desempenho, uma vez que eles não foram projetados visando arquiteturas assimétricas.

Este trabalho propõe o desenvolvimento de um escalonador de laços paralelos que usa um algoritmo adaptativo para melhor adaptar uma carga de trabalho à ambientes de processamento assimétrico. Tal adaptabilidade é alcançada de forma inconsciente em relação aos recursos de processamento: o escalonador não diferencia processadores com características distintas, abrindo mão de ajustes específicos para processadores com desempenhos diferentes. Os objetivos específicos deste trabalho são:

- Apresentar um estudo na literatura de trabalhos anteriores que visavam a criação de escalonadores adaptativos, que serviram como base para o desenvolvimento do novo escalonador.

- Propor o desenvolvimento de um novo escalonador adaptativo, que possibilite adaptabilidade a diferentes ambientes de execução (respeitando a arquitetura à qual a aplicação foi construída), roubo de trabalho e baixo sobrecusto de escalonamento;

- Avaliar o desempenho dos escalonadores em um conjunto de benchmarks paralelos bem-estabelecidos em ambientes assimétricos reais e comparar o seu desempenho com os escalonadores existentes.

Esta dissertação está organizada da seguinte maneira: o Capítulo 2 fornece conceitos importantes abordados pelo trabalho, como processadores multinúcleo assimétricos e seu impacto no desempenho de aplicações paralelas, algoritmos adaptativos e escalonadores de laços paralelos existentes que hoje compõem o estado da arte, ao final apresentando os trabalhos relacionados encontrados na literatura. Os algoritmos e detalhes da implementação do escalonador proposto estão presentes no Capítulo 3. Uma análise de desempenho do escalonador sobre aplicações científicas e de *benchmarks* em plataformas assimétricas foi descrita no Capítulo 3.6. Por fim, o Capítulo 4 apresenta uma discussão sobre este trabalho e os resultados obtidos.

# 2 FUNDAMENTAÇÃO TEÓRICA

Esse capítulo apresenta as definições de Processadores Multinúcleo Assimétricos e algoritmos adaptativos de acordo com a literatura, e introduz alguns escalonadores de laços paralelos já existentes. Ao final, uma relação de trabalhos relacionados encontrados na literatura é apresentada e comentada.

#### 2.1 ARQUITETURAS PARALELAS

O advento da multiplicação de unidades de processamento ( $Processing\ Unit$ , em inglês – PU) no mesmo chip trouxe muitas mudanças no campo de computação de alto desempenho. Dependendo de algoritmo e arquitetura, é possível acelerar uma aplicação por volta de N vezes para N núcleos idênticos, podendo inclusive ultrapassar-se esse valor se o desenvolvedor souber como otimizar seus trechos de código visando especificidades da arquitetura. Extrair o máximo de desempenho de uma arquitetura para uma aplicação é uma tarefa de importância vital para a indústria e áreas de pesquisa científica, como trabalhos de sequenciamento de DNA, previsão do tempo, simulação de dinâmica de fluídos, entre outros.

Processadores multinúcleo podem possuir diferenças entre seus núcleos componentes: diferenças em frequência, consumo de energia, tamanho e hierarquia de cache, especialidade, ISA e micro-arquitetura podem ser encontradas internamente em muitos tipos de processadores. À essa classe de processadores a classificação de arquitetura heterogênea é atribuída.

# 2.1.1 Taxonomia de Arquiteturas Paralelas

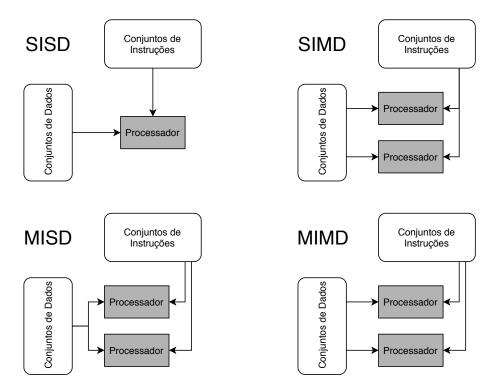

Flynn e Rudd (1996) desenvolveram uma classificação para arquiteturas de computadores baseados em como eles se comportam levando em consideração dados e instruções. Assumindo que um computador executa um conjunto de instruções em um conjunto de dados e que este computador pode possuir múltiplos fluxos dos mesmos, quatro grandes classes podem ser desenhadas através da combinação dessas características:

SISD – Single Instruction and Single Data (uma instrução e um dado, em inglês). Modelo clássico de processamento sequencial, correspondente à arquitetura de Von Neumann, apesar de poder possuir características de processamento concorrente (FLYNN; RUDD, 1996). O modelo de Von Neumann pode ser considerado limitado

em termos de desempenho, uma vez que ele projeta o uso de um único barramento para ler e/ou escrever instruções e dados (BACKUS, 1978);

- MIMD *Multiple Instructions and Multiple Data* (múltiplas instruções e múltiplos dados, em inglês), pode ser considerado o modelo clássico de paralelismo, onde cada PU pode conter seu próprio conjunto de instruções e processá-las concorrentemente a outras PUs em cima de seu próprio conjunto de dados. Este modelo é facilmente encontrado na maioria dos CPUs produzidos, e pode ser identificado em MICs (acrônimo para "muitos núcleos integrados", em inglês) e inclusive GPGPUs (acrônimo para "unidade de processamento gráfico de propósito geral", em inglês) (DIETZ; YOUNG, 2010), assim como pode ser emulado em arquiteturas SIMD (DIETZ; COHEN, 1992);

- SIMD Single Instruction and Multiple Data (uma instrução e múltiplos dados, em inglês), um único fluxo de instruções é executado sobre múltiplos fluxos de dados. Este modelo foi popularizado pela adoção de sua implementação em GPGPUs, e pode ser encontrado também em unidades vetoriais dentro de núcleos de arquiteturas de CPU modernas;

- MISD Multiple Instructions and Single Data (múltiplas instruções e um dado, em inglês), modelo incomum onde várias instruções são executadas sobre o mesmo conjunto de dados. Há poucas aplicações práticas conhecidas desta classe de arquitetura, como por exemplo o uso de arrays sistólicos para encontrar o maior divisor comum de dois polinômios diferentes de zero (BRENT; KUNG, 1984).

A Ilustração 2.1 mostra um diagrama-exemplo que ilustra conceitualmente as quatro classes descritas. Este trabalho foca em arquiteturas MIMD, que origina problemas de escalonamento por definição, uma vez que cada processador pode realizar tarefas distintas.

## 2.2 PROCESSADORES MULTINÚCLEO ASSIMÉTRICOS

Quando este trabalho faz referências a AMPs, a definição referenciada é a proposta por Fedorova et al. (2009): Um processador multinúcleo assimétrico consiste de núcleos que possuem o mesmo conjunto de instruções de arquitetura (*Instruction Set Architecture* – ISA) mas entregam desempenhos diferentes e tem características de consumo energético diferentes. É importante enfatizar que AMP está situado em uma subclasse de processamento heterogêneo: todo AMP tem habilidade de processamento heterogêneo por definição, mas nem todos processamento heterogêneo se é realizado por um AMP, como casos de execuções concorrentes entre CPUs e GPUs ou MICs, por exemplo.

Entretanto é comum que a definição ou a nomenclatura de AMP varie de autor para autor. Como constatado por Mittal (2016) em sua pesquisa, apesar do fato que "Processa-

Ilustração 2.1 – Diagrama da Taxonomia de Flynn e Rudd (1996).

Fonte: Adaptado de (FLYNN; RUDD, 1996).

dor Multinúcleo Assimétrico" é o termo mais largamente usado para descrever processadores com tipos de núcleos heterogêneos, diversos autores usam terminologias diferentes para descrever AMPs dependendo da origem da assimetria.

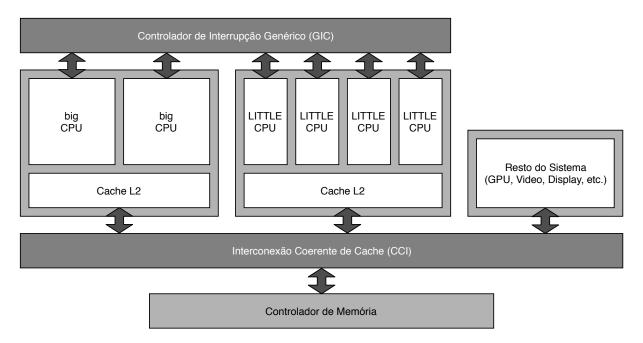

## 2.2.1 ARM big.LITTLE™

A tecnologia ARM big.LITTLE consiste em uma arquitetura de AMPs que foram projetados para atender uma demanda de computação móvel que era guiada por dois fatores (ARM Limited, 2013b): 1) se fazia necessária um entrega maior de desempenho para suportar aplicações móveis de última geração – que crescem em complexidade e peso computacional – mas sem ultrapassar alguns limites térmicos; 2) um consumo muito baixo de energia, uma vez que esses processadores na maioria dos casos são alimentados com baterias pequenas com tempo de duração de carga limitado.

Essa arquitetura de processamento heterogêneo é composta de dois tipos de núcleo: "LITTLE", projetados para máxima eficiência energética, e "big", projetados para prover um maior desempenho computacional. Usualmente esses processadores são coerentes e compartilham do mesmo ISA (ARM Limited, 2013b). Dessa forma uma tarefa pode ser dinamicamente alocada para qualquer dos dois tipos de núcleo dependendo dos requisitos instantâneos da mesma. Diferenças nas micro-arquiteturas internas o permite

prover diferentes taxas de consumo energético e desempenho: os tipos de núcleo podem apresentar essas diferenças em atributos como tamanho e tipo de pipelines, frequência, tamanho de cache L1 e L2, número de núcleos, entre outros. O uso de uma interconexão coerente de cache permite ao sistema garantir a coerência dos dados nas memórias cache e demais dispositivos do sistema sem precisar realizar acessos constantes e lentos à memória principal (Ilustração 2.2).

Ilustração 2.2 – Diagrama exemplo de um processador multinúcleo assimétrico: um sistema big.LITTLE típico com 2 núcleos rápidos (big) e 4 núcleos lentos (LITTLE).

Fonte: Adaptado de (ARM Limited, 2013b).

#### 2.2.2 Efeitos da Assimetria no Desempenho

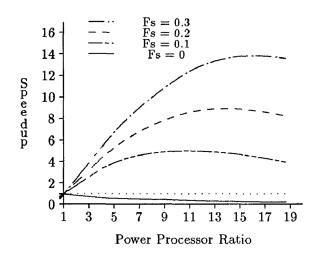

A inclusão de núcleos mais rápidos em sistemas – trazendo consigo assimetria e heterogeneidade – surge com a promessa de, além de possibilitar mais desempenho em tarefas especializadas de cada tipo de núcleo, permitir um ganho teórico de desempenho em aplicações paralelas. Com base nas leis de Amhdal – a fração sequencial de um programa paralelo domina o tempo de execução e limita as vantagens que arquiteturas paralelas podem obter (AMDAHL, 1967) – e de Grosch – o desempenho do computador aumenta conforme o quadrado de seu custo (GROSCH, 1953) –, e baseados em modelos de teoria de filas, Menascé e Almeida (1990) concluem que se é possível extrair mais desempenho de arquiteturas paralelas heterogêneas em aplicações paralelas quando comparadas à arquiteturas paralelas homogêneas de mesmo custo de fabricação. Quão maior for a fração de trabalho sequencial na aplicação, maior a aceleração paralela teórica da arquitetura he-

terogênea em relação à homogênea, devido aos núcleos rápidos que podem ser usados para acelerar trechos de códigos sequenciais em uma aplicação (MENASCÉ; ALMEIDA, 1990; BALAKRISHNAN et al., 2005). O Gráfico 2.1 apresenta o ganho teórico potencial de uma arquitetura heterogênea com um núcleo rápido em relação à uma arquitetura homogênea de mesmo custo, com 1106 núcleos: o ganho de desempenho aumenta juntamente com a porcentagem de trabalho sequencial.

Gráfico 2.1 – Aceleração teórica paralela de uma arquitetura paralela heterogênea em relação à uma homogênea de mesmo custo. O eixo vertical corresponde à aceleração paralela e o eixo horizontal à escala que o núcleo rápido é mais rápido que os núcleos lentos. O rótulo  $F_S$  denota diferentes valores de fração de trabalho sequencial.

Fonte: Extraído de (MENASCÉ; ALMEIDA, 1990).

Entretanto tal estimativa leva em consideração um escalonamento ótimo, algo muito difícil de acontecer no mundo real, devido a inúmeras variáveis que podem afetar o desempenho das aplicações (MENASCÉ; ALMEIDA, 1990). Com a premissa que uma assimetria entre processadores pode levar a um desbalanceamento de carga em um sistema paralelo, Balakrishnan et al. (2005) conduziram um estudo que investigou o impacto da assimetria no desempenho de arquiteturas multinúcleo. Os autores avaliaram os tempos de execução de diferentes aplicações em um ambiente com assimetria induzida via alteração de frequências em conjuntos de núcleos de um SMP. Duas questões principais tiveram suas respostas buscadas no estudo: 1) Se a assimetria pode ter um impacto negativo no desempenho, e se o mesmo pode ser previsto em um AMP; 2) Quais métodos podem ajudar aplicações que tenham perdas de desempenho devido à essa assimetria.

Através de avaliações de diferentes tipos de aplicação, que variaram de aplicações comerciais a ferramentas de desenvolvimento, os autores chegaram às seguintes conclusões, dentre outras:

A assimetria em sistemas afeta a previsibilidade de comportamento de cargas de trabalho, tornando-as menos escaláveis. O efeito aumenta proporcionalmente ao total de concorrência no sistema;

Um escalonador ciente da assimetria a nível de sistema operacional pode ajudar algumas aplicações a variarem menos seus tempos de execução, ao realizar migrações de cargas de trabalho para núcleos mais rápidos quando estes estão ociosos. Entretanto, isso não se aplica a aplicações que tem um controle maior do escalonamento de suas tarefas paralelas;

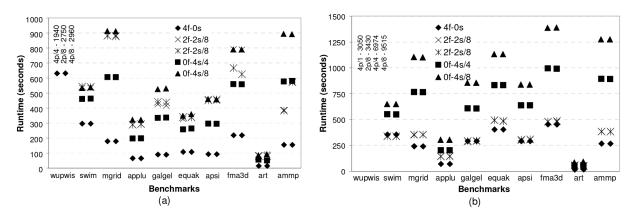

Como ressaltado pelo trabalho, o escalonamento de cargas de trabalho quando realizado internamente pela própria aplicação também tem impacto no desempenho. Dentre as aplicações testadas havia um conjunto de benchmarks (SPEC OMP) que utiliza OpenMP como *back-end*. A maioria desses benchmarks utilizados apresentaram desempenhos contra-intuitivos, como exibido no Gráfico 2.2(a). Os resultados mostram que não há como ter previsibilidade no desempenho, ao passo que um dos benchmarks (ammp) apresentou tempos menores para combinações de núcleos que possuiam um maior poder computacional quando comparado a outras combinações. O motivo para esse comportamento é a forma como os benchmarks escalonavam seus laços paralelos, fazendo divisões estáticas de tamanho igual entre os processadores.

Gráfico 2.2 – Tempo de execução do conjunto de benchmarks SPEC OMP. (a) Tempo com a implementação original do SPEC; (b) Tempo com escalonamento dinâmico. Um rótulo no formato nf-ms/escala denota uma configuração com n núcleos rápidos e m núcleos lentos executando a 1/escala da velocidade dos núcleos rápidos. O poder computacional normalizado total para uma configuração é dado por n+m/escala. Uma configuração 2f-2s/8 possui um poder computacional teórico maior que uma configuração 0f-4s/4, mas apresenta tempos de execução maiores para o benchmark ammp em (a), devido à má ditribuição da carga de trabalho entre as threads.

Fonte: Extraído de (BALAKRISHNAN et al., 2005)

Em uma situação dessas, podem existir dois tipos de comportamento para escalonamento estático:

1. Se cada *thread* for associada à um núcleo específico e/ou o sistema operacional não possui um escalonador ciente da assimetria: núcleos lentos tendem a demorar mais

- para terminarem seus trabalhos e acabam fazendo com que núcleos rápidos fiquem ociosos esperando, uma vez que os laços paralelos do OpenMP possuem barreiras implícitas no seu final, forçando uma etapa de sincronização global entre as *threads*;

- 2. Se o sistema operacional é ciente da assimetria e migra todo o trabalho de um núcleo lento para um núcleo rápido que estava ocioso: tal migração tende a reduzir o tempo total de execução, uma vez que o tempo de espera será menor pois o núcleo rápido tender a terminar a tarefa mais rapidamente. Entretanto, tal abordagem ainda não utiliza todo o poder computacional disponível, uma vez que ainda haverão núcleos ociosos ainda que relativamente mais lentos esperando pelo término do trabalho de outros núcleos.

O problema com previsibilidade de desempenho foi solucionado ao aplicar um escalonador dinâmico aos laços paralelos, conforme pode ser observado no Gráfico 2.2(b). Entretanto, apesar de eliminar os efeitos da assimetria, tal abordagem acabou aumentando o tempo total de execução. Esse aumento substancial nos tempos pode ser culpa da forma como o escalonador dinâmico do OpenMP trabalha (seção 2.4.1).

#### 2.3 ALGORITMOS ADAPTATIVOS

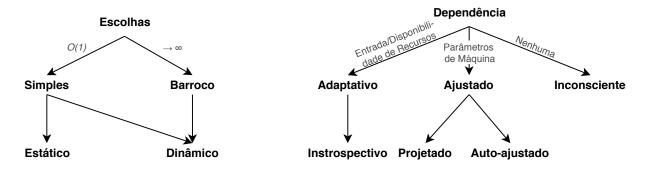

Este trabalho usa a definição de algoritmos adaptativos criada por Cung et al. (2006), que definem algoritmos adaptativos em função de algoritmos híbridos. De acordo com os autores, por definição, um algoritmo é híbrido quando existe uma escolha em alto nível entre pelo menos dois algoritmos diferentes, ambos com habilidade de resolver o mesmo problema. A escolha visa um aumento de desempenho da execução, dependendo dos dados de entrada/saída e dos recursos computacionais. Um algoritmo híbrido pode ser

simples (simple) – O(1) escolhas são realizadas independentemente de características da entrada como tamanho, por exemplo. Embora apenas um número constante de escolhas seja feito, cada escolha pode ser usada um número ilimitado de vezes durante a execução.

**barroco** (baroque) – o número de escolhas não é limitada, depende da entrada.

Embora as escolhas em um algoritmo híbrido simples possam ser definidas estaticamente antes de qualquer execução, algumas opções em algoritmos híbridos barrocos são necessariamente computadas em tempo de execução. As opções podem ser executadas com base nos parâmetros da máquina. Mas existem algoritmos eficientes que não baseiam suas escolhas em tais parâmetros. Distinguem-se as seguintes classes de algoritmos híbridos de acordo com a maneira como as escolhas são computadas:

**inconsciente** (*oblivious*) – O fluxo de controle do algoritmo não depende nem dos valores particulares das entradas nem das propriedades estáticas dos recursos.

ajustado (tuned) – Decisões estratégicas são tomadas com base em recursos estáticos, como parâmetros específicos da memória ou recursos heterogêneos dos processadores em uma computação distribuída. Um algoritmo ajustado é projetado (engineered) se uma escolha estratégica for inserida com base em uma mistura de análise e conhecimento da máquina de destino e dos padrões de entrada. Um algoritmo híbrido é auto-ajustado (self-tuned) se as opções são automaticamente computadas por um algoritmo.

adaptativo (adaptive) – evita qualquer parametrização específica de máquina ou memória. As decisões estratégicas são tomadas com base na disponibilidade de recursos ou nas propriedades dos dados de entrada, ambas descobertas em tempo de execução (como processadores inativos). Um algoritmo adaptativo é introspectivo (introspective) se uma decisão estratégica for tomada com base na avaliação do desempenho do algoritmo na entrada fornecida até o ponto de decisão.

A Ilustração 2.3 resume a classificação no formato de um diagrama.

Ilustração 2.3 – Classificação de algoritmos híbridos.

Fonte: Adaptado de (CUNG et al., 2006)

## 2.4 ESCALONADORES DE LAÇOS PARALELOS

Muitas bibliotecas e APIs para habilitar processamento paralelo já foram implementadas, com diferenças entre si como linguagem de programação suportada, sistemas operacionais suportados, especialidades distintas, hardware específico, etc. Algumas destas bibliotecas oferecem ao desenvolvedor uma forma abstraída de dividir o trabalho de laços de repetição entre diferentes *threads*, com algumas focando em descarregar códigos e dados para PUs externas (OpenMP Architecture Review Board, 2018; EDWARDS; TROTT;

SUNDERLAND, 2014; GREGORY; MILLER, 2012; DURAN et al., 2011; OpenACC Organization, 2019) ou usando em conjunto com a CPU (DOLBEAU; BIHAN; BODIN, 2006), ou de forma distribuída (DIMAKOPOULOS; HADJIDOUKAS, 2011), ou na forma como os dados são acessados (EDWARDS; TROTT; SUNDERLAND, 2014; GREGORY; MILLER, 2012), ou em metodologias diferentes como uso de troca de mensagens (KALÉ; KRISH-NAN, 1993) ou de criação de tarefas (OpenMP Architecture Review Board, 2018; Intel Corporation, 2019b; DIMAKOPOULOS; HADJIDOUKAS, 2011; DURAN et al., 2011; Intel Corporation, 2019a). Poucas dessas soluções focam na solução de problemas induzidos pela assimetria de processadores dentro da mesma CPU, com a justificativa de não ser o foco da ferramenta ou na confiança da entrega de desempenho de um escalonador dinâmico simples, como no caso do OpenMP. Este trabalho usará duas soluções existentes a fim de comparar o desempenho da solução proposta: OpenMP, que é o mais próximo de um padrão industrial devido a sua adesão por fabricantes de compiladore, a simplicidade de sua API e por suportar diferentes arquiteturas, e Intel TBB, uma biblioteca que se baseia no uso de tarefas e tem como principal objetivo a distribuição dinâmica de cargas de trabalho de forma eficiente.

## 2.4.1 OpenMP

OpenMP (do inglês *Open Multi-Processing*, ou Multi-processamento aberto) é uma interface de programação de aplicações (API) aberta que provê um modelo de programação compacto, mas ainda assim flexível, para Fortran, C e C++ disponível para desenvolvedores de aplicações paralelas em memória compartilhada para múltiplas plataformas e sistemas operacionais. Consiste em um conjunto de diretivas de compilador, rotinas de biblioteca e variáveis de ambiente (CHAPMAN; JOST; VAN DER PAS, 2007). Sua especificação fornece formas de paralelizar laços e diferentes escalonadores para tal. Tais escalonadores podem ser especificados através do uso da cláusula schedule em combinação com a diretiva de paralelização de laços for (Ilustração 2.4).

```

#pragma omp parallel for [schedule(<escalonador>[,<grao>])]

for (/* parametros do laco */) { /* corpo do laco */ }

```

Ilustração 2.4 – Caso exemplo de paralelização de laço com OpenMP. A cláusula schedule é opcional, assim como a especificação de um tamanho para grão.

Fonte: Adaptado de (OpenMP Architecture Review Board, 2018).

A diretiva parallel especifica a criação de uma região paralela – um bloco de código que explicitamente terá 1 ou mais *threads* executando em paralelo – e pode ser declarada separadamente ou em combinação com a diretiva for, como no exemplo. Em

geral, cada compilador possui uma implementação diferente da API. Mas em praticamente todas as implementações mais recentes há suporte aos três principais tipos de escalonadores: static, dynamic e guided.

- static Escalonador estático. Quando especificado, o intervalo de iterações é dividido em t porções de tamanho aproximadamente iguais para t threads em uma região paralela OpenMP. Se um tamanho de grão g é especificado, o intervalo é dividido em porções de tamanho g e os mesmos são distribuídos através um algoritmo de roundrobin para cada thread (OpenMP Architecture Review Board, 2018). Seu uso pode proporcionar bom desempenho em SMPs e laços com carga de trabalho regular, e potenciais percas de desempenho em cenários que distoem desse.

- dynamic Escalonador dinâmico. Quando especificado, as iterações são distribuídas dinâmicamente em pedaços entre as *threads*. Cada *thread* extrai um pedaço do intervalo, executa, e então requisita outro pedaço, até que não restem mais pedaços a serem processados (OpenMP Architecture Review Board, 2018). As iterações são disponibilizadas internamente em uma fila global centralizada, onde as *threads* concorrentemente extraem porções conforme necessário (DURAND et al., 2013). Cada pedaço contém *g* iterações conforme especificado pelo programador através do tamanho do grão, exceto pelo último pedaço da fila, que pode conter menos iterações. Quando nenhum tamanho de grão é especificado, o tamanho definido por padrão é 1 (OpenMP Architecture Review Board, 2018). Tal abordagem pode ajudar a alcançar melhores desempenhos em cenários onde o escalonador estático pode se apresentar ineficiente.

- guided Escalonador 'guiado'. Quando especificado, as iterações são distribuidas dinâmicamente em porções de tamanho variado entre as *threads*. Cada *thread* extrai um pedaço do intervalo, executa, e então requisita outro pedaço, de tamanho menor ou igual ao anterior, até que não restem mais porções, como no escalonador dinâmico (OpenMP Architecture Review Board, 2018). O tamanho do grão é definido por  $\lceil r/t \rceil$ , onde r é o total de iterações restantes do intervalo original e t é o total de *threads* em execução na região paralela. Esse tamanho consequentemente diminui conforme a execução avança até um tamanho mínimo g, especificado pelo usuário no tamanho do grão. Se nenhum grão for especificado, g=1 por padrão (OpenMP Architecture Review Board, 2018).

Além desta diretiva com três escalonadores distintos, o OpenMP ainda oferece mais uma forma de paralelizar laços através de sua API, com a diretiva taskloop (Ilustração 2.5).

Diferentemente da diretiva anterior, a diretiva taskloop divide o trabalho do laço em um grupo de tarefas explícitas a serem computadas por cada *thread* na região paralela. Para um intervalo de iterações de tamanho s, a API prevê a criação de k tarefas

```

#pragma omp taskloop [num_tasks(qtdTarefas)] [grainsize(grao)]

for (/* parametros do laco */) { /* corpo do laco */ }

```

Ilustração 2.5 — Caso exemplo de paralelização de laço com a diretiva taskloop do OpenMP. A cláusula num\_tasks é opcional, assim como a especificação de um tamanho para grão na cláusula grainsize.

Fonte: Adaptado de (OpenMP Architecture Review Board, 2018).

com tamanho mínimo de grão  $g \geq 1$ . A quantidade de tarefas e/ou o tamanho do grão mínimo podem ser especificadas atráves das cláusulas  $\mathtt{num\_tasks}$  e  $\mathtt{grainsize}$ , respectivamente. Se nenhuma das cláusulas for especificada o valor padrão para as mesmas é dependente da especificada na implementação do compilador. As implementações providas pelos compiladores GCC e Clang definem o tamanho padrão de grão como 1. A forma como as tarefas são criadas também é dependente da implementação. O compilador GCC cria as tarefas linearmente, enquanto o Clang cria de forma recursiva enquanto o número de tarefas a serem criadas for maior que um limiar, então passando a criar de forma linear. Esse limiar pode ser estipulado pelo usuário através da variável de ambiente KMP\_TASKLOOP\_MIN\_TASKS, caso contrário é definido por padrão através de um função heurística. Na versão 8 do compilador Clang essa heurística é dada por min(t\*10,256), onde t é o número de threads da região paralela.

#### **2.4.2 Intel TBB**

Intel TBB (do inglês *Threading Building Blocks*, ou Blocos de Construção de *Threads*) é uma biblioteca C++ para programação paralela que oferece um conjunto de métodos e *templates* C++ para a criação de aplicações paralelas. Com foco no uso de tarefas ao invés de *threads* explicitas, o TBB possibilita alcançar bons desempenhos e escalabilidade ao dinamicamente redistribuir essas tarefas entre PUs (CONTRERAS; MARTONOSI, 2008).

Laços paralelos são suportados no TBB através dos métodos tbb::parallel\_for e tbb::parallel\_reduce, com o último possuindo suporte para operações de redução. A llustração 2.6 mostra as assinaturas de métodos que permitem a paralelização de laços.

O Intel TBB possui 4 tipos de escalonadores – que a biblioteca denomina como *partitioners* (particionadores, em inglês) – para laços paralelos (Intel Corporation, 2019b):

tbb::auto\_partitioner Escalonador automático. Esse escalonador adapta os intervalos de iterações de acordo com os recursos disponíveis em tempo de execução. O worker (trabalhador) mestre cria uma tarefa com todo o intervalo de iterações. Esta

```

// limites do intervalo com duas variaveis

tbb::parallel_for(inicio, fim, corpo_laco [, escalonador]);

// limites do intervalo atraves de um tbb::blocked_range

tbb::parallel_for(tbb::blocked_range<tipo>(inicio, fim [, grao]), corpo_laco [, escalonador]);

// reducao paralela

valor = tbb::parallel_reduce(tbb::blocked_range<tipo>(inicio, fim [, grao]), identidade, corpo_laco, corpo_reducao [, escalonador]);

```

Ilustração 2.6 — Caso exemplo de paralelização de laço com biblioteca Intel TBB. inicio e fim denotam o início e o final do intervalo de iterações e possuem tipo tipo. grao é um valor para cálculo de grão. corpo\_laco representa o bloco de código interior de um laço a ser executado em paralelo, pode ser uma função comum ou uma função lambda, assim como corpo\_reducao. escalonador representa um objeto de escalonador que pode ser opcionalmente passado para as funções. Por fim, identidade representa o valor inicial de um dado a ser reduzido, valor o valor final, e o tipo tbb::blocked\_range uma classe do TBB para manipulação de intervalos em uma ou mais dimensões.

Fonte: Adaptado de (Intel Corporation, 2019b).

tarefa então subdivide-se recursivamente criando novas tarefas até uma profundidade máxima D, empilhando-as na deque local de tarefas do worker e dividindo o intervalo pela metade a cada recursão. Quando o worker consome por completo uma tarefa, ele retira uma nova tarefa do final de seu deque e subdivide-a até a profundidade máxima se necessário. O comportamento é similar a um algoritmo de busca em profundidade.

Um worker, quando ocioso e com o deque vazio, escolhe aleatoriamente uma vítima e rouba sua tarefa do início do deque de tarefas, que geralmente contém a primeira metade do trabalho da vítima que ainda não fora dividido. O ladrão então subdivide-o até uma profundidade D+1 (com exceção do primeiro roubo de cada worker, onde não há um acréscimo na profundidade). O acréscimo na profundidade é refletido no worker vitima, que também acaba aumentando sua profundidade máxima em 1.

A profundidade D é determinada pela fórmula  $D=5+k \ \mathrm{com} \ k=\lfloor \log_2 N \rfloor -1$  sendo  $k\geq 0$  e N o número de *threads*. Caso um grão não seja especificado, o tamanho da porção de trabalho mínima é 1. Entretanto é possível especificar um valor c para o tamanho mínimo, por meio de um objeto  $\mathtt{tbb}:\mathtt{blocked\_range}$ , sendo que cada porção de trabalho sequencial g será tal que  $g\geq c/2$ . Quando um escalonador não é especificado, este é utilizado por padrão $^1$ ;

tbb::simple\_partitioner Escalonador 'simples'. A forma de divisão de trabalho entre *threads* também é recursiva, e também há roubo de trabalho, entretanto não há um

<sup>&</sup>lt;sup>1</sup>padrão desde a versão 2.2 da biblioteca

limite de profundidade como no escalonador automático. Apesar disso, o escalonador respeita o tamanho do grão: para um grão g, a porção de trabalho sequencial c será tal que  $g/2 \le c \le g$ . Quando um tamanho de grão não é especificado (através do uso de um objeto tbb:blocked\_range), o tamanho do grão por padrão é determinado como 1. Sua implmentação é similar à implementação do framework CilkPlus² (depreciado), também desenvolvido pela Intel, com a diferença que o CilkPlus adotava uma abordagem work-first (quando uma tarefa é criada, o worker suspende e coloca a tarefa corrente na pilha de tarefas para então executar a nova tarefa), diferente da abordagem help-first (coloca imediatamente a tarefa nova na pilha de tarefas) adotada pelo Intel TBB;

tbb::static\_partitioner Escalonador estático. Praticamente igual ao escalonador estático do OpenMP. Busca dividir o intervalo o mais igualmente possível entre todas as *threads*, mas respeitando a fórmula  $c \geq max(g/3, n/t)$ , onde n é o tamanho do intervalo original e t o número de *threads* TBB.

tbb::affinity\_partitioner Escalonador com respeito à afinidade. Em suma idêntico ao escalonador automático, com a diferença que o histórico de atribuições de sub-intervalos à *threads* é salvo no objeto do particionador para ser reutilizado posteriormente, buscando um melhor aproveitamento da cache.

#### 2.5 TRABALHOS RELACIONADOS

Alguns trabalhos foram conduzidos para desenvolver escalonadores adaptativos em diferentes contextos. Esta seção apresenta trabalhos encontrados na literatura que tomam uma direção similar ao foco deste trabalho, mas que eventualmente divergem, seja por não se dirigirem a AMPs ou sistemas heterogêneos, ou seja por não focarem na paralelização de laços.

Menon (2016) apresentou diferentes algoritmos adaptativos para balanceamento de carga inter e intra-nodo, para laços paralelos e tarefas com dependência. Inicialmente ele apresenta a GrapevineLB, uma estratégia para balanceamento de carga de laços paralelos completamente distribuída. Ela baseia o balanceamento sobre uma representação parcial do estado global do sistema. Possui dois estágios: propagação e transferência. No estágio de propagação, informações de carga de trabalho sobre PUs subcarregadas são propagadas para PUs sobrecarregadas através de um algoritmo epidêmico, selecionando aleatoriamente outras PUs a receberem e repassarem a informação a diante. A etapa

<sup>&</sup>lt;sup>2</sup><www.cilkplus.com>

de propagação pode ter um número limite de rodadas, ou um controle de quem já recebeu a informação. Na etapa de transferência, processadores subcarregados a receberem carga podem ser escolhidos aleatoriamente, ou aleatoriamente com uso de uma função de distribuição, onde processadores subcarregados mais próximos da média de carga do sistema tem menor probabilidade de receberem transferências de carga. Uma modificação, que os autores nomearam de Grapevine+, dá a habilidade à uma PU subcarregada de rejeitar trabalho caso perceba que ficará sobrecarregada. A forma de determinar se uma PU está sobre ou subcarregada é através de uma comparação de sua carga com a carga média. Entretanto, o autor não apresenta como esta média é obtida ou estipulada. Ambas as estratégias, implementadas em Charm++, apresentaram tempos menores que outras estratégias em ambientes homogêneos distribuídos de 4096 a 131072 unidades de processamento. O autor também propõe outro balanceador de carga para ambientes distribuídos, mas com foco na criação de tarefas locais, tirando a exclusividade da divisão em processos e comunicação por meio de troca de mensagens da proposta anterior. Nessa abordagem o intervalo de iterações é inicialmente dividido igualmente entre os nodos no sistema distribuído e, dentro de cada nodo, dividido recursivamente com a criação de tarefas paralelas, em uma abordagem muito similar à do framework CilkPlus. Para esta abordagem foram usadas diferentes implementações - dependendo da aplicação utilizada para testes – combinando bibliotecas como Charm++, OpenMP, MPI e Adaptive MPI. Com um foco maior no balanceamento de carga interno de cada nodo, essa abordagem conseguiu menores tempos de execução que as implementações originais de cada aplicação, conseguindo acelerações paralelas maiores que 2 vezes. O autor apresenta essa abordagem como uma boa alternativa para ambientes heterogêneos ou aplicações com maiores desbalanceamentos de carga. Apesar da menção à ambientes heterogêneos, todos as avaliações desta estratégia e da estratégia anterior visaram somente ambientes homogêneos distribuídos: o trabalho não apresenta resultados sobre o impacto de sua abordagem em ambientes heterogêneos ou com heterogeneidade induzida (p.ex. desativação de alguns núcleos, alteração de frequência via DVFS, entre outros). Além disso, há uma preocupação por parte do autor com o sobrecusto da criação excessiva de tarefas durante a decomposição do problema. Algumas medidas são tomadas para prevenção (retenção na criação de tarefas com base na ocupação das PUs), mas o impacto das mesmas não é avaliado no trabalho.

Meadows e Ishikawa (2017) trabalharam na otimização do CCS-QCD – uma aplicação Stencil 3D – usando tarefas OpenMP para multiplexar computações com comunicações MPI. A aplicação originalmente definia *threads*/núcleos exclusivos para gerenciar as comunicações MPI, mas essa abordagem acarretava na sub-utilização desses núcleos na maior parte do tempo relacionado à computação necessária dos dados. Eles decidiram implementar um versão alternativa do escalonador de laço de forma similar à diretiva taskloop do OpenMP – dividindo blocos de iterações em tarefas –, uma vez que a pró-

pria implementação da diretiva não estava otimizada na versão do compilador utilizado no trabalho (Intel C++ Compiler XE 17.0.2.174). A implementação é também equivalente à implementação do framework CilkPlus. Essa abordagem mostrou que o escalonador de tarefas padrão do OpenMP do compilador utilizado consumia em média 10% do tempo de execução somente com escalonamento. Os autores então decidiram implementar seu próprio escalonador de tarefas, chamado untasking, com a biblioteca Intel TBB, onde cada thread mantém sua própria fila de iterações. O laço principal para escalonamento de tarefas de um thread desenfileira tarefas (blocos de iterações) da fila da thread até a fila estar vazia, então busca nas filas das outras threads uma tarefa para roubar. Os autores não entram em detalhes sobre as políticas de roubo aplicadas no escalonador. A implementação final do untasking exibiu uma melhoria de desempenho da ordem de 1.6x quando comparado à implementação original do CCS-QCD, e 1.2x à implementação alternativa ao taskloop. O CPU utilizado na avaliação foi um Intel Xeon Phi 7250 com 68 núcleos. O objetivo do trabalho era muito específico – otimizar uma única aplicação – o que fez a abordagem final convergir em uma solução muito específica para a aplicação, ainda que alguns conceitos podem ser extraídos do projeto do escalonador.

Em busca de realizar um balanceamento dinâmico de carga ao mesmo tempo em que leva afinidade de memória em conta em arquiteturas NUMA (Non-Uniform Memory Access, Acesso Não-Uniforme à Memória), Durand et al. (2013) trabalharam em um escalonador de laços que visava prover meios de balancear a carga de laços irregulares respeitando localidade de memória, uma fonte comum de problemas de desempenho em arquiteturas NUMA. Os autores estenderam o escalonador para respeitar a localidade de memória ao definirem uma ordem de prioridade para selecionar vítimas em um roubo de trabalho: o escalonador faz os workers localizados em um mesmo banco de memória trabalharem em iterações contíguas entre si. Quando necessário, workers ociosos roubam trabalho de workers em núcleos que pertençam ao mesmo nó NUMA. Se não há trabalho restante para ser roubado no nó NUMA local, o worker ocioso emite uma requisição de roubo para uma vítima selecionada aleatoriamente no escopo inteiro da máguina. A runtime libGOMP foi extendida para suportar os escalonadores propostos diretamente na cláusula schedule do OpenMP. O desempenho do escalonador proposto foi avaliado em quatro benchmarks diferentes e alcançou uma aceleração paralela de 2.35 sobre o escalonador estático do OpenMP, ainda que gaste relativamente mais tempo com sobrecustos do escalonador.

Mór (2015) desenvolveu uma aproximação da primitiva originalmente adaptativa cilk\_for da biblioteca CilkPlus para processar paralelamente estruturas de dados similares à listas. Um *worker* recebe um *iterator* referente a um elemento da lista ao invés de um índice do laço. O algoritmo é adaptativo e muito similar ao algoritmo proposto por Meadows e Ishikawa (2017). O autor mescla o algoritmo adaptativo com um algoritmo de avaliação polinomial e simula sua execução em dois tipos diferentes de estratégia de

seleção de vítima para roubo de trabalho: aleatória e *clock* mínimo (um *worker* ocioso seleciona um *worker* ativo com o menor valor de *clock*). As simulações mostraram que o número de roubos bem-sucedidos necessários é menor para a estratégia de *clock* mínimo, uma vez que um *worker* pode acabar realizando roubos mais significativos – i.e. roubar de *workers* que tenham mais trabalho restante. O objetivo do trabalho não era avaliar o desempenho do algoritmo de escalonamento em qualquer tipo de ambiente, apesar do número de roubos estar diretamente relacionado à sobrecusto paralelo, e consequentemente ao desempenho como um todo.

Traoré et al. (2008) apresentou um escalonador paralelo adaptativo para algoritmos STL, com roubo de trabalho. A implentação usa uma lista distribuída por *worker*, ao invés de uma *deque* (fila duplamente terminada), a fim de limitar o sobrecusto com criações de tarefas. O escalonador também possui uma etapa de mescla para algoritmos que necessitem de operações pós-computações, como reduções. O algoritmo *deque-free* é composto de um micro-laço (o curso dos ladrões de acordo com a ordem sequencial do trabalho roubado) e um nano-laço (a computação do trabalho). Roubos são feitos recursivamente, confiando a seleção de vítimas à *runtime* de tarefas. O escalonador foi implementado usando a *runtime* Kaapi e comparado com versões do Intel TBB e MCSTL, apresentando melhores tempos médios quando comparado com as outras opções na maioria dos casos.

Todos os trabalhos mencionados até aqui não exploraram e/ou relataram o desempenho e o comportamento de suas soluções em ambientes assimétricos.

Chronaki et al. (2017) propuseram duas abordagens de escalonamento de tarefas que visavam sistemas com processamento assimétrico: CPATH e HYBRID. Essas políticas de escalonamento dinâmicas reduzem o tempo total de execução tanto ao detectar o caminho maior ou crítico do grafo dinâmico de dependências de tarefas, quanto ao encontrar o executor mais recente de uma tarefa. A implementação do CPATH separa tarefas em ordem de prioridade (críticas ou não-críticas) e atribui tarefas com maior prioridade para núcleos mais rápidos. Ele também usa tempos de execução de tarefas previamente conhecidos para determinar heuristicamente caminhos críticos no grafo de dependências de tarefas. A implementação HYBRID é derivada da CPATH, mas somente leva tempos de execução em consideração se eles estiverem disponíveis, possibilitanto menores sobrecustos que o CPATH. Ambos os escalonadores foram implementados usando o modelo de programação OmpSs e tiveram seus desempenhos comparados com dois escalonadores existentes (CATS e HEFT) e o algoritmo de busca em largura. A avaliação de desempenho foi executada em uma placa ODROID-XU3 (veja seção 3.7.2) e em ambientes simulados com um número total de 16 e 32 núcleos, variando o número de núcleos rápidos. Os resultados mostraram que o escalonador HYBRID alcançou um desempenho equivalente ao escalonador CATS, sendo um pouco melhor em um benchmark de decomposição QR.

Apesar de visar melhorar desempenho em processadores assimétricos, o trabalho foca no desenvolvimento de escalonadores de tarefas, enquanto este trabalho foca em es-

calonadores de laços paralelos. Uma tarefa, na abordagem do autor, é uma unidade de trabalho computacional que é substancialmente diferente de um laço paralelo: tarefas normalmente não podem ser sub-divididas, e podem possuir atributos como prioridades que as diferem entre si. Os escalonadores propostos pelo trabalho fazem uso de heurísticas baseadas em históricos de tempo de execução, o que não é uma abordagem vantajosa para laços paralelos, uma vez que manter históricos de tempo de execução por iteração ou blocos de iterações pode ser extremamente custoso em termos de uso de memória para a *runtime*. Além disso, a implementação não pode ser classificada como adaptativa, mas como ajustada (veja seção 2.3), desde que o algoritmo conhece características específicas dos núcleos – i.e. o algoritmo sabe se o núcleo é rápido/big ou lento/LITTLE.

# 2.6 SUMÁRIO

Este Capítulo apresentou uma breve introdução sobre arquiteturas paralelas e sua taxonomia, seguida da definição de processadores multinúcleo assimétricos, um exemplo existente encontrado atualmente no mercado (ARM big.LITTLE) e o impacto potencialmente negativo da assimetria induzida pelos mesmos no desempenho de aplicações. É apresentada a definição de algoritmos adaptativos e exemplos de bibliotecas referentes ao estado da arte para escalonamento de laços paralelos, descrevendo escalonadores existentes em implementações do padrão OpenMP e na biblioteca Intel TBB. Ao final, trabalhos relacionados aos temas escalonamento adaptativo e escalonamento em AMPs são apresentados, e suas diferenças em relação ao trabalho proposto são ressaltadas.

Os tópicos abordados neste Capítulo ajudam a ilustrar a necessidade de uma solução para distribuição da carga computacional de laços paralelos em AMPs, tema não abordado em sua integridade pela literatura existente. O Capítulo a seguir apresenta a proposta e detalhes da implementação de um escalonador de laços paralelos que distribua a carga dos mesmos de forma que vise se adaptar melhor a ambientes que possuam capacidade de processamento assimétrica.

#### 3 ESCALONADOR ADAPTATIVO

Este Capítulo apresenta a proposta de um escalonador que permite adaptar a carga de trabalho de um laço paralelo em AMPs. As seções a seguir apresentam detalhes da construção interna do escalonador, bem como seus algoritmos de extração de trabalho e como sua implementação foi conduzida através do uso da linguagem de programação C++ e do paradigma de orientação à objetos.

# 3.1 LAÇO PRINCIPAL DO ESCALONADOR

Ao usar uma aproximação derivada de (DURAND et al., 2013), um escalonador adaptativo seguiria três etapas maiores para computar um laço paralelo:

- 1. Divide o intervalo original de iterações entre as threads em sub-intervalos;

- 2. Cada thread extrai sequencialmente uma porção de trabalho de seu sub-intervalo;

- 3. Quando sem trabalho, uma *thread* procura uma *thread* vítima com trabalho restante e rouba uma porção de trabalho para si, retornando à etapa 2. Se não poder roubar trabalho, encerra sua execução.

Como cada aplicação pode conter um número arbitrário de laços paralelos, essas etapas seriam repetidas a cada invocação de laço. A partir de um ponto de vista externo, esses passos podem ser interpretados como o laço principal de execução de uma ferramenta de escalonamento de laços paralelos. Usando esses passos como pilares sólidos, a construção de um escalonador pode ser proposta.

O escalonador proposto por este trabalho é composto por, além de alguns métodos para invocação de laços paralelos, um *Coordenador* responsável por instanciar, lançar e coordenar as *threads* utilizadas pelo escalonador. Durante a execução da aplicação, as *threads* criadas ficam a espera de *Trabalhadores* contendo a descrição do trabalho a ser realizado.

Um Trabalhador representa uma entidade responsável por computar uma parte do trabalho, sendo necessariamente associado à uma *thread* específica. Quando um método para criação de um laço paralelo é invocado, as informações referentes ao laço (intervalo de iteração e corpo do laço) são inseridas em Trabalhadores instanciados pelo método, e os mesmos são posteriormente transmitidos para o Coordenador, para que o mesmo possa invocar métodos de inicialização dos Trabalhadores e dar início à execução do laço.

Um Trabalhador é composto basicamente de uma trava de software e dois subintervalos de iterações:

- Um sub-intervalo maior, que representa a parte referente à este Trabalhador/thread do intervalo original do laço a ser paralelizado. Seus limites inferior e superior são delimitados pelas variáveis membro first e last, respectivamente;

- Um sub-intervalo menor, que representa um porção de trabalho, extraída do sub-intervalo maior, para ser processada de forma sequencial pela thread a qual o Trabalhador está vinculado. Essa extração deve, por definição, ser o mais livre de travas quanto for possível, de forma a eliminar sobrecustos paralelos com o processo de extração. Seus limites inferior e superior são delimitados pelas variáveis membro chunk\_begin e chunk\_end, respectivamente.

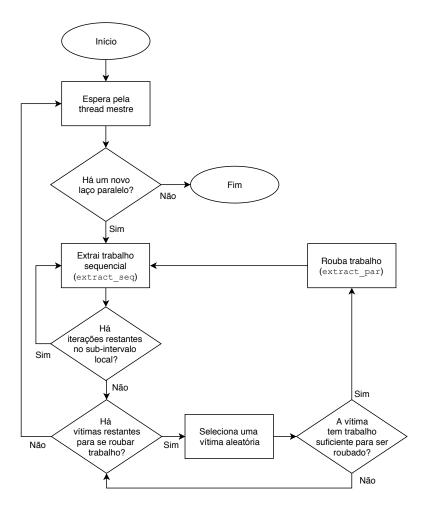

Cada thread possui um ciclo de vida. Quando a aplicação é lançada, as threads são iniciadas e ficam à espera de trabalho. Quando um trabalho é recebido através de um Trabalhador, as threads dão início ao laço principal de cada Trabalhador, que consomem o trabalho através de extrações sequenciais sobre o mesmo, até o momento que o trabalho local ao Trabalhador termine, fazendo com que cada Trabalhador passe a tentar roubar trabalho (extração paralela) de outros Trabalhadores. Se não há trabalho restante, a thread descarta o Trabalhador e espera pela thread mestre sinalizar se há um novo trabalho (fornecendo novos Trabalhadores, que representam um novo laço paralelo) ou se ela deve encerrar seu ciclo de vida (geralmente ao final da execução da aplicação).

A escolha entre os dois tipos de extração de trabalho (sequencial e paralela) configuram o algoritmo referente ao laço principal do escalonador como um algoritmo híbrido. Com base em um algoritmo de roubo de trabalho, o escalonador pode permitir um melhor escalonamento da carga computacional de um laço paralelo: redistribuindo adaptativamente de forma dinâmica porções do intervalo de iterações referente a um laço entre PUs com diferentes desempenhos, visando diminuir ao máximo o tempo ocioso de cada PU do sistema, e sem realizar distinções entre diferentes PUs com diferentes desempenhos, tornando o algoritmo adaptativo por definição.

A llustração 3.1 ilustra o ciclo de vida de uma *thread* típica, enquanto a llustração 3.2 apresenta um exemplo visual de como uma extração sequencial ocorre concorrentemente à uma extração paralela (roubo de trabalho) em um mesmo sub-intervalo;

Ilustração 3.1 – Fluxograma do ciclo de vida de uma thread.

Fonte: O autor.

```

chunk_size * k

(a)

chunk_size * k

(b)

chunk_size * (k+1)

chunk_size * k

(m - (chunk_size * k)) / 2

(m - (chunk_size * k)) / 2

(c)

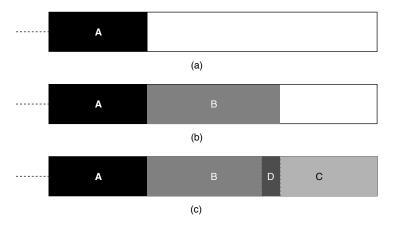

```

Ilustração 3.2 — Caso exemplo de extração de trabalho em um sub-intervalo de tamanho m. São ilustrados três estados subsequentes: (a) k porções de trabalho de tamanho chunk\_size já foram extraídos pela *thread* dona do sub-intervalo; (b) Uma outra *thread* rouba uma determinada quantia do sub-intervalo (no exemplo, metade do que resta); (c) A *thread* extrai mais chunk\_size iterações do seu sub-intervalo.

Fonte: Adaptado de (MÓR, 2015).

### 3.2 ALGORITMOS DE EXTRAÇÃO SEQUENCIAL E PARALELA

Como informado na seção anterior, o escalonador proposto escolhe em tempo de execução entre dois métodos de extração para extrair trabalho para cada Trabalhador: uma extração sequencial e uma extração paralela. Esses métodos consistem em uma adaptação do protocolo THE do *framework* Cilk (FRIGO; LEISERSON; RANDALL, 1998) para uso com intervalos de iterações.

O algoritmo presente na Ilustração 3.3 apresenta o processo de extração de trabalho sequencial. Através de sucessivas chamadas ao método EXTRACT\_SEQ, um Trabalhador extrai trabalho sequencial de seu sub-intervalo maior (delimitado por first e last). A porção de trabalho extraída corresponde a um total de iterações determinado por chunk\_size e delimitado por chunk\_begin e chunk\_end.

Ilustração 3.3 – Escalonador Adaptativo – Algoritmo de Extração de Trabalho Sequencial

```

1: function EXTRACT_SEQ

old first \leftarrow first

2:

chunk\_begin \leftarrow MIN(first + chunk\_size, last)

3:

if chunk\_begin > chunk\_end then

4:

first \leftarrow chunk \ begin

5:

if chunk\_begin < last then

⊳ Confirma se a extração é válida

6:

7:

chunk\_end \leftarrow first

chunk\_begin \leftarrow old\_first

8:

return TRUE

9:

end if

10:

first \leftarrow old \ first

▷ Conflito: desfaz e trava a si próprio

11:

end if

12:

LOCK(self)

13:

chunk \ begin \leftarrow first

14:

if chunk\_begin < last then

15:

first \leftarrow chunk\_end \leftarrow last

16:

end if

17:

18:

UNLOCK(self)

19:

return chunk\_begin < first

20: end function

```

Fonte: O autor.

São realizados dois testes para validar a extração: (1) (linha 4) se o novo limite inferior do sub-intervalo maior (temporariamente em chunk\_begin) é maior que o limite superior antigo da último porção de trabalho extraída (chunk\_end), e (2) (linha 6) se o novo limite inferior do sub-intervalo maior (ainda em chunk\_begin) é menor que o limite superior do sub-intervalo maior (last).

Caso um conflito seja detectado durante a extração de trabalho sequencial - isto

é, um Trabalhador concorrente rouba uma parte da porção de trabalho que seria extraída – o Trabalhador desfaz as modificações parciais (linha 11) e trava a si próprio (linha 13). Uma vez travado, o seu sub-intervalo maior não pode ser modificado concorrentemente por nenhum outro Trabalhador. A extração então é realizada e o método EXTRACT\_SEQ retorna um valor lógico indicando se uma porção de trabalho de tamanho válido foi obtida (linha 19). Essa situação só acontecerá uma vez por sub-intervalo maior: caso um conflito seja detectado e/ou seja a última extração do sub-intervalo maior. Um sub-intervalo roubado é considerado um novo sub-intervalo maior. A ilustração 3.4 mostra um exemplo de conflito durante o processo de extração.

Ilustração 3.4 – Caso exemplo de um conflito durante extração de trabalho. São ilustrados três estados subsequentes: (a) O Trabalhador dono do sub-intervalo já havia extraído A iterações; (b) O Trabalhador dono do sub-intervalo se prepara para extrair outras B iterações; (c) Concorretemente, um outro Trabalhador tenta roubar C iterações, entretanto o intervalo representado por C intersecciona com B, gerando uma região D que pode ter trabalho duplicado caso o conflito não seja tratado.

Fonte: O autor.

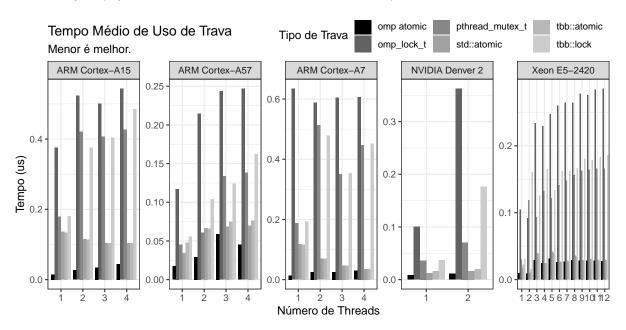

A extração visa ser o mais livre de travas o quanto possível e, para tal, definiu-se uma ordem de operações para extrair e, concorrentemente, roubar um bloco contíguo de iterações de um sub-intervalo. As linhas 4 e 5 do algoritmo presente na Ilustração 3.3 e as linhas 8 e 9 do algoritmo na Ilustração 3.5 são o ponto-chave para tal: a ordem das instruções assegura a corretude das operações em ambientes com consistência de memória sequencial. Entretanto, a maioria das arquiteturas paralelas modernas não suportam consistência de memória sequencial porque a adesão à seu suporte pode resultar em uma diminuição geral de desempenho, uma vez que requer a execução sequencial de instruções relacionadas à memória (GEORGOPOULOS, 2016). Desse modo, para assegurar a corretude do algoritmo, se faz necessária a inserção de barreiras de memória entre esses pares de linha. Nesta implementação, foi definido o uso de tipos atômicos atomic da linguagem C++ para os membros first e last, pois são projetados para não causarem condição de corrida em dados e podem ser usados para sincronizar acessos à memória entre threads com um custo computacional menor que travas tradicionais (ISO, 2013).

O Algoritmo 3.5 ilustra como um roubo de trabalho é efetuado. Um Trabalhador ladrão segue quatro passos para roubar trabalho de outro Trabalhador, quando necessário:

- Ele escolhe aleatoriamente uma vítima victim (linha 3), testa se a mesma possui um sub-intervalo válido e tenta travá-la (linha 4) para que, caso consiga, nenhum outro Trabalhador possa roubá-la enquanto ela não for liberada;

- 2. O tamanho do roubo (steal\_size) é determinado de acordo com o tamanho do subintervalo da vítima (método GET\_STEAL\_SIZE) (linha 5);

- São feitos testes para verificar se o valor referente ao novo início do sub-intervalo (new\_first, variável temporária) está dentro do sub-intervalo atual da vítima (linhas 7 e 9);

- 4. o roubo é efetuado (linhas 8 e 12-15).

Ilustração 3.5 – Escalonador Adaptativo – Algoritmo de Extração de Trabalho Paralelo (Roubo de Trabalho). Todas as variáveis precedidas por victim representam membros do Trabalhador vítima.

```

1: function EXTRACT_PAR

while CAN STEAL(workers) do

2:

victim \leftarrow \texttt{SELECT} \ \ \texttt{VICTIM}(workers)

3:

if victim.last > victim.first \text{ AND } \text{CAN\_LOCK}(victim) then

4:

steal\_size \leftarrow \texttt{GET\_STEAL\_SIZE}(victim)

5:

6:

new \ first \leftarrow victim.last - steal \ size

if victim.last > new\_first \text{ AND } victim.first \leq new\_first \text{ then}

7:

victim.last \leftarrow new\_first

8:

if victim.first > victim.last then

9:

victim.last \leftarrow new\_first + steal\_size

10:

else if steal\_size > 0 then

11:

first \leftarrow new \ first

12:

13:

last \leftarrow new \ first + steal \ size

UNLOCK(victim)

14:

return TRUE

⊳ Roubo bem sucedido

15:

end if

16:

UNLOCK(victim)

17:

end if

18:

end if

19:

20:

end while

return FALSE

▶ Não consegue roubar: encerra execução

21:

22: end function

```

Fonte: O autor.

O ladrão não espera pela liberação da trava da vítima (linha 4) com o objetivo de não ficar ocioso. Se a trava não estiver disponível, ele então seleciona outra vítima. O

número de vezes que o método EXTRACT\_PAR é invocado determina o sobrecusto paralelo que o escalonador introduzirá. Esse sobrecusto paralelo faz-se inexistente em execuções com somente uma *thread*, uma vez que toda concorrência é eliminada. Caso um conflito durante a extração seja detectado, a ação é desfeita (linha 10) e o ladrão desiste da vítima, liberando sua trava (linha 17). O processo se repete até que o algoritmo identifique que nenhum outro Trabalhador tenha trabalho restante para roubar (linha 2).

# 3.3 OTIMIZAÇÃO

Esta abordagem de escalonamento descentraliza a distribuição de carga de trabalho e reduz a concorrência paralela total quando em comparação com o escalonador dinâmico do OpenMP. Além disso, este trabalho propõe uma forma de extração sequencial das porções de trabalho o mais livre de travas quanto possível. Pode-se variar os seguintes parâmetros neste escalonador em busca de tempos ótimos:

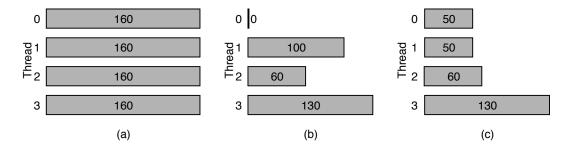

Tamanho do sub-intervalo inicial de cada thread: Algumas abordagens como a do framework CilkPlus e da biblioteca Intel TBB (escalonador aumomático e simples) apostam em uma concentração inicial do intervalo de iterações em uma thread, delegando a distribuição da carga inicialmente para os algoritmos de roubo de trabalho. Experimentos preliminares apontam que essa abordagem não é muito vantajosa quando combinada com o escalonador proposto, trazendo um aumento no tempo de escalonamento: as threads precisam sincronizar o início de sua execução para garantir que todas tenham acesso à mesma função (leia-se corpo de laço paralelo) e intervalo de iterações, tornando redundante o custo com roubo de trabalho no início da execução. O escalonador implementado divide de forma igualitária o intervalo original entre as threads, de forma similar à como os escalonadores estáticos do OpenMP e TBB fazem.

**Tamanho da porção de trabalho sequencial:** Este trabalho propõe três abordagens diferentes para definição do tamanho das porções de trabalho a serem extraídas para processamento sequencial:

- fixa o número de iterações a serem processadas por vez é sempre fixo;

- 2. fracionada a quantia de iterações é representada por uma fração do tamanho original do sub-intervalo de cada Trabalhador. Tal abordagem garante que cada sub-intervalo terá uma quantia máxima constante de porções a serem extraídas;

- 3. logarítmica calcula-se o logaritmo na base 2 do tamanho do sub-intervalo original de cada Trabalhador. O uso de um valor logarítmico permite que o número

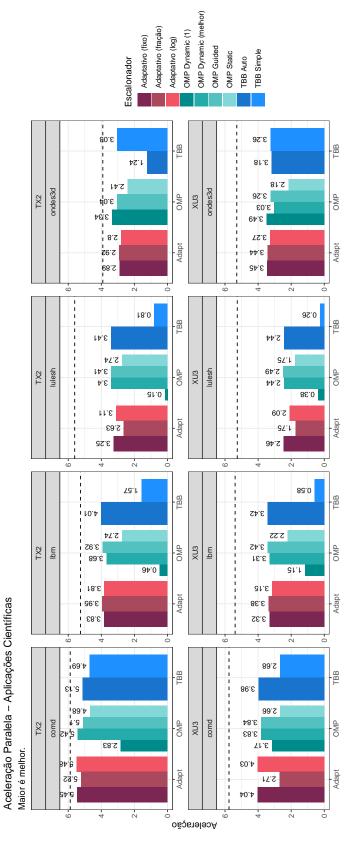

de porções de trabalho a serem extraídas aumentem junto com o tamanho da porção conforme o tamanho do sub-intervalo, buscando um maior dinamismo.